# **IR3220S**

## FULLY PROTECTED H-BRIDGE FOR D.C. MOTOR

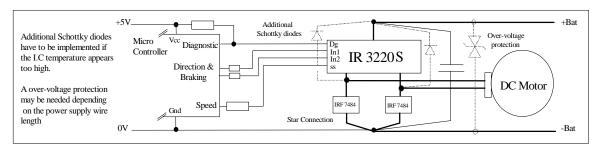

The IR3220S is a fully protected dual high side switch I.C that integrates an H-bridge motor controller with two very efficient high side MOSFETs in a single 20-pin package. The IR3220S combines with the two low side IRF7484Q MOSFETs as few as 10 external passive components to provide a complete, fully operational and fully protected H-bridge control actuator with forward, reverse, braking and non-braking modes without the need of a micro-controller.

### **Functional Description**

The high side switches provide the direction capability and the Hbridge protection. The low side MOSFETs bring the flexibility by offering the high frequency switching ability. Therefore, crude start-up of the motor is avoided and replaced by a smooth and stress-less speed ramp-up.

The IR3220S features shoot-through protection for each leg, H-bridge logic control, soft-start sequence and over-current / over-temperature shutdown protections. Two input signals (IN1 & IN2) select the operating modes while the PWM soft-start sequence cycles the corresponding active low side MOSFET in order to limit the motor in-rush current. The soft-start sequence is programmed by an RC time constant and reset itself automatically. Thanks to the inner PWM oscillator, the IR3220S can also be the final stage of an overall torque or speed loop. If needed, an external clock may force the H-bridge switching operation. This can be combined with low frequency PWM operation through the IN1(2) inputs.

The IR3220S is a Co-pack IPS product offering very low Rds(on) and a high level of functionality and protection. Its open architecture and programmability helps the designer to optimize each motor drive upon the application requirements at a very low cost. For automotive actuators, the motor is kept shorted even during the low consumption sleep mode. Shoot-through protection, overtemperature & over-current shutdowns, self-adaptive dead-time and PWM circuitries are described in details in the *AN 1032* Application Note. A general purpose method to help rating the soft-start sequence as well as layout and thermal considerations are also covered. Finally, a 6A DC motor actuator with a PCB size down to 1 Inch² is suggested in the document.

#### **Features**

Programmable PWM In-rush Current Limitation (e.g. 18A)

6 A Continuous Current Capability without Heat Sink (2 x 13 m $\Omega$ )

Over-Temperature (165 °C) and Over-Current (30A) Protections

20 kHz PWM Oscillator Embedded

Low & High Frequency Switching Operation (self adaptive dead-time)

Easy Speed / Torque Control (analog duty cycle input)

Braking / Non-Braking Modes

Sleep Mode (braking) for Automotive Actuator

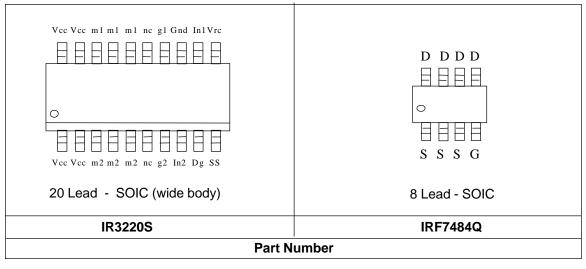

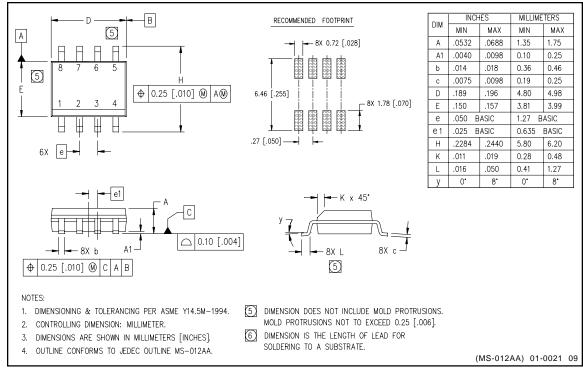

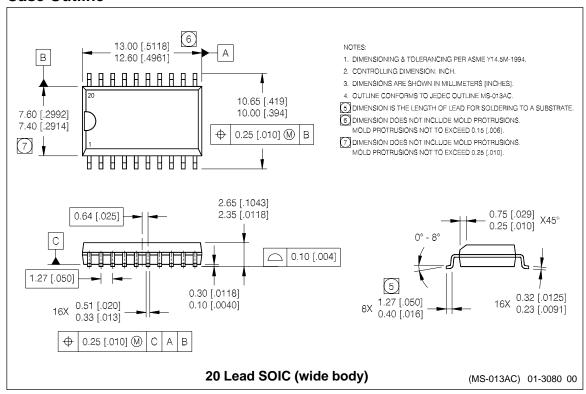

## **Packages**

8-Lead SOIC IRF7484Q

20-Lead SOIC (wide body)

www.irf.com 1

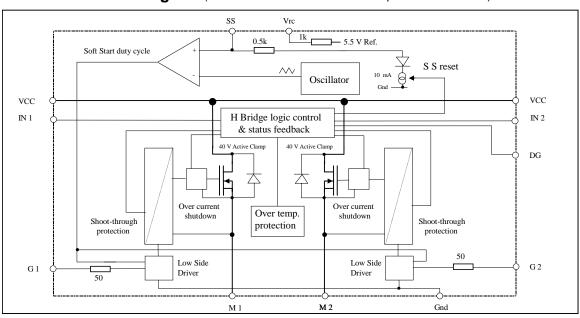

# Functional Block Diagram (see AN-1032 for a detailed description of each block)

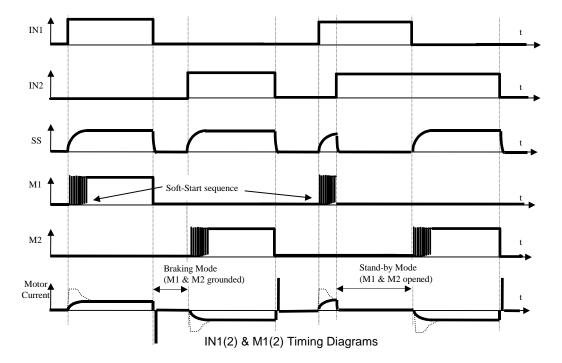

Thanks to the self-adaptive dead-time circuitry, the low side MOSFET of each leg is driven in the opposite phase of the high side one without any conflict. Thus, the single IN1 signal turns on the leg M1 (and IN2, the output M2). Consequently, when both IN1 and IN2 are low, the quiescent state of the H-bridge is the Braking Mode (the two low side MOSFETs on). The over-temperature circuitry and the two over-current protections (one per leg) protect the IC and flag the DG pin. The thermal shutdown also covers the body diode overheating. Fault conditions are reset by cycling the corresponding IN1(2) input. Each leg appears independent so that the PWM soft-start management is greatly simplified and makes the 20kHz oscillator block almost a separate function. The positive input of the PWM comparator is accessible on the SS pin. An external analog voltage or a RC network can either drive the duty cycle. It has to be said that a clock signal (< 20 kHz) applied on this input will directly drive the low side MOSFETs. A 5V voltage source is embedded in the I.C ( switched off while in the sleep mode ) so that no additional power supply is needed for the soft-start RC time constant. Its capacitor is discharged through the ''SS reset '' circuitry every time IN1 equals IN2. Thus, the soft-start sequence is ready to operate whichever the formerly braking mode was.

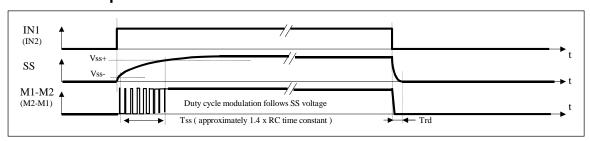

#### **Soft-Start Sequence**

#### **Truth Table**

| IN1 | IN2 | MODES                                   | DG | HS1 | LSS1 | HS2 | LSS2 | SS reset |

|-----|-----|-----------------------------------------|----|-----|------|-----|------|----------|

| L   | L   | Stand-by with braking - sleep mode**    | Н  | OFF | ON   | OFF | ON   | ON       |

| L   | Н   | Forward rotation (normal operation)     | Η  | OFF | ON*  | ON  | OFF  | OFF      |

| L   | Н   | Forward rotation (protection triggered) | L  | OFF | ON*  | OFF | OFF  | OFF      |

| Н   | L   | Reverse rotation (normal operation)     | Н  | ON  | OFF  | OFF | ON*  | OFF      |

| Н   | L   | Reverse rotation (protection triggered) | L  | OFF | OFF  | OFF | ON*  | OFF      |

| Н   | Ι   | Stand-by without braking                | Η  | OFF | OFF  | OFF | OFF  | ON       |

<sup>\*</sup> During Soft-start sequence, the low side part is switching.

The IR 3220S over-current is set at 30A which is low enough to protect the whole application. The soft-start RC time constant has to be designed in order to keep the maximum in-rush current below the I shutdown (application worst case - see AN 1032). The total switching sequence is about 1.4 times the RC time constant. A smoother start-up is even achievable by slightly increasing the RC values. However, the soft-start sequence should remain short enough not to trip the over-temperature protection (Tj while free-wheeling). The truth table shows that the soft-start sequence can be interrupted at any time. But a minimum time is needed prior to any change in the direction or re-start of a new SS sequence. Actually, the capacitor of the RC network has to be discharged and the motor fully stopped first otherwise the over-current protection might trip during the next turn-on.

The protections turn off the high side MOSFETs so that no braking sequence follows the fault detection. Both IN1 and IN2 have to go low for a minimum time in order to reset the fault circuitry. When both inputs are back to the low level, the H-bridge is in the braking mode and the motor shorted. In this mode, no protection is activated and the peak current due to the braking is not monitored. After 300 ms, the I.C sleep mode is activated and the consumption is reduced down to few micro-amps. The low side gate drivers keep the gates high so the motor remains shorted. When using end switches, the I.C goes into the low consumption mode as soon as the mechanical stop are reached. When interfacing such switches directly to the IR 3220S, de-bouncing RC networks have to be implemented on the input pins in order to prevent false over-current detection.

<sup>\*\*</sup> Protections are reset in this mode

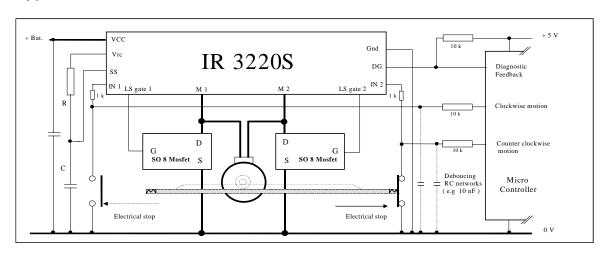

# **Typical Connection**

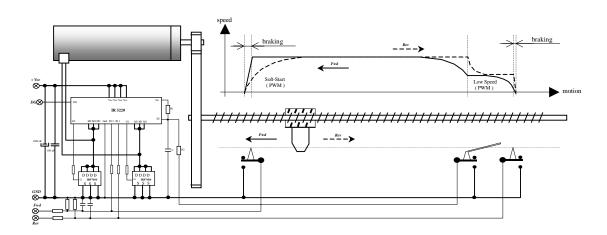

The PWM generator is based on a 3V saw-tooth oscillator. The soft-start sequence takes advantage of the RC charge profile in order to perform a smooth duty cycle variation. When the SS pin is below 1.2V, no PWM signal is sent to the low side MOSFETs. When it exceeds 4.2V, they are permanently ON. By designing the proper RC network, the start-up can either be very slow without any in-rush current or, fast and efficient by shortening the PWM sequence. In addition to the quiescent braking mode, the IR 3220S is able to open the four MOSFETs simultaneously if the mechanical load requires its natural slow-down (stand-by mode without braking). The four modes and their corresponding DC motor current profiles are summarized in the Timing Diagram.

Over-load protection is achieved thanks to the I.C temperature shutdown protection. By using the recommended part number and the proper cooling, the whole H-bridge is protected by the IR 3220S's inner over-temperature circuitry (see AN 1032). A micro-controller is able to directly drive the PWM duty cycle by forcing a 0 to 5V voltage on the SS pin (e.g. through a 10K resistor). Thus, closing a speed or torque control loop for advanced applications becomes very easy. Since the low side MOSFETs are the only ones switching, the IR 3220S body diodes offer the freewheeling path to the motor. The power dissipated in each body diode while switching may appear high enough to trip the over-temperature protection. For permanent switching operation, external Schottky diodes should be implemented between each output (M1 & M2) and the VCC pin.

#### **Permanent Switching Operation**

(without external RC time constant)

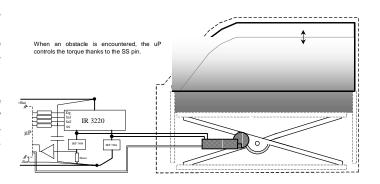

Copper plates added to the footprints will improve the cooling. However, the low side MOSFETs should always remain colder and thermally independent from the IR 3220S. The power path has to be designed carefully and shall include both a decoupling capacitor (e.g. 100 nF ceramic) and a reservoir capacitor (e.g. Cres ( uF). = I pk soft-start (A) x 25). The window-lifter is a good example where the IR 3220S's PWM ability greatly enhances the application. The current is monitored thanks to a shunt and sent back to the micro-controller which takes over the torque control loop (anti-pinch function).

In addition, the soft-start sequence provides a smooth motion of the window. Torque or speed controls are also achievable without any micro-controller. With a few additional components, the IR 3220S can be the '' power stage'' of an overall analog control loop. The SS pin is then used as the PWM duty cycle input (continuous switching operation requires high cooling capability)

For actuators, the PWM Soft Start sequence helps reduce the speed before reaching the end switches. Therefore, the braking time is very short and the actuator final position is then accurate and repeatable as shown hereunder. Mechanical stops under torque control are also possible by controlling the motor current through the PWM duty cycle.

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are referenced to Gnd lead. (Tambient = 25°C unless otherwise specified). Symbols with (2) refer to M2 output.

| Symbol               | Parameter                                                      | Min.    | Max.    | Units |  |  |  |

|----------------------|----------------------------------------------------------------|---------|---------|-------|--|--|--|

| Vm1 (2)              | Maximum M1 (M2) voltage (active clamp)                         | Vcc-37  | Vcc+0.3 |       |  |  |  |

| V <sub>in1</sub> (2) | Maximum IN 1 (IN 2) voltage                                    | -0.3    | 5.5     | V     |  |  |  |

| Vcc/gnd              | Maximum Vcc pin to GND pin voltage                             | -0.3    | 45      |       |  |  |  |

| I in1 (2)            | Maximum IN1 (IN 2) current                                     | -1 10 m |         |       |  |  |  |

| Vg1 (2)              | Maximum Gate 1 ( Gate 2 ) voltage                              | -0.3    | 7.5     |       |  |  |  |

| Vss                  | Maximum SS voltage                                             | -0.3    | 5.5     | V     |  |  |  |

| Vrc                  | Maximum Vrc voltage                                            | -0.3    | 5.5     |       |  |  |  |

| Irc                  | Maximum output current of the Vrc pin                          |         | 1       | mA    |  |  |  |

| Vdg                  | Maximum diagnostic output voltage                              | -0.3    | 5.5     | V     |  |  |  |

| ldg                  | Maximum diagnostic output current                              | -1      | 10      | mA    |  |  |  |

| Isd cont.            | Diode max. permanent current (Rth=80℃/W) (1)                   | _       | 2.0     |       |  |  |  |

|                      | (Rth=60℃/W) (1)                                                | _       | 3.0     | Α     |  |  |  |

| Isd pulsed           | Diode max. pulsed current (1)                                  | _       | 15      |       |  |  |  |

| ESD 1                | Electrostatic discharge ( human body model C=100pF, R=1500Ω)   | _       | 4       |       |  |  |  |

| ESD 2                | Electrostatic discharge ( machine model C=200pF, R=0Ω, L=10μH) | _       | 0.5     | kV    |  |  |  |

| PD                   | Maximum power dissipation ( Rth = 80℃/W )                      | _       | 1.5     | W     |  |  |  |

| TJ max.              | Max. storage & operating junction temperature                  | -40     | +150    | °C    |  |  |  |

| TL                   | Lead temperature ( soldering 10 seconds )                      | _       | 300     |       |  |  |  |

| Vcc/gnd max.         | Maximum Vcc to GND voltage (0.4 s - single pulse)              | _       | 60      | V     |  |  |  |

| lg1 (2) max.         | Maximum transient gate current (Ton < 5μS)                     | _       | 100     | mA    |  |  |  |

| lg1 (2) avg.         | Maximum average gate current                                   | _       | 10      |       |  |  |  |

<sup>(1)</sup> Limited by junction temperature.

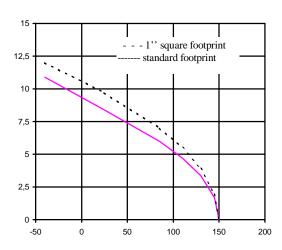

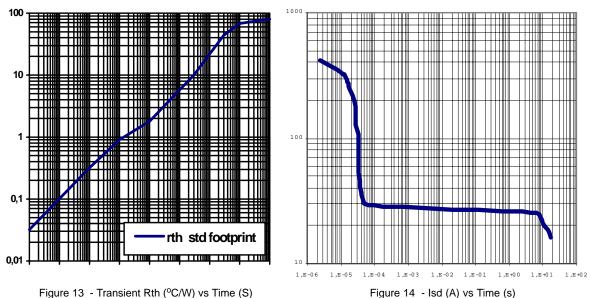

# **Thermal Characteristics**

| Symbol            | Parameter                                                 | Тур. | Max. | Units |

|-------------------|-----------------------------------------------------------|------|------|-------|

| R <sub>th</sub> 1 | Junction to ambient thermal resistance (std footprint)    | 80   | _    | °C/W  |

| R <sub>th</sub> 2 | Junction to ambient thermal resistance (1" sq. footprint) | 60   | _    | 0,11  |

Recommended Operating Conditions

These values are given for a quick design. For operation outside these conditions, please consult the application notes.

| Symbol               | Parameter                                             | Min. | Max. | Units |

|----------------------|-------------------------------------------------------|------|------|-------|

| Vcc                  | Continuous Vcc voltage (2)                            | 8    | 28   |       |

| V <sub>in1</sub> (2) | High level IN 1 (IN 2) input voltage                  | 4    | 5.5  | V     |

| V <sub>in1</sub> (2) | Low level IN 1 (IN 2) input voltage                   | -0.3 | 0.9  |       |

| lout Ta=85℃          | Continuous output current (Std footprint - Tj = 150℃) | _    | 6.0  | Α     |

| lout Ta=105℃         | Continuous output current (Std footprint - Tj = 150℃) | _    | 5.0  |       |

| R in                 | Recommended resistor in series with IN pin            | 0.5  | 5    |       |

| R dg                 | Recommended pull-up resistor on DG pin                | 10   | 20   | kΩ    |

| R                    | Soft-Start resistor                                   | 20   | 200  |       |

| С                    | Soft-Start capacitor                                  | 0.1  | 3.3  | μF    |

| R gate               | Recommended gate resistor for Low Side Switch         | 0    | 50   | Ω     |

| Lm min.              | Minimum motor inductance required                     | 10   | _    | μН    |

#### **Static Electrical Characteristics**

$(T_j = 25^{\circ}C, V_{CC} = 14V \text{ unless otherwise specified.})$

| Symbol          | Parameter                            | Min. | Тур. | Max. | Units  | Test Conditions        |

|-----------------|--------------------------------------|------|------|------|--------|------------------------|

| Rds1 on         | ON state resistance Tj = 25°C        | _    | 11   | 13   | - mΩ   |                        |

| Rds2 on         | ON state resistance Tj = 150°C       | _    | 18   | 22   | 11162  | Vin1,2 = 5V,1m1,2 = 5A |

| Vcc oper.       | Functional voltage range             | 5.5  | _    | 35   |        |                        |

| Vclamp1 (2)     | Vcc to M1 (M2) clamp voltage         | 37   | 40   | 48   | V      | Id =10mA see Figs.1,2  |

| Vf1 (2)         | Body diode 1 (2) forward voltage     | _    | 0.9  | _    |        | Id = 5A, Vin1,2 = 0V   |

| IM1 (2) leakage | M1 (M2) output leakage current       | _    | 10   | 50   |        | Vm1, 2 = 0V; Tj = 25°C |

| Icc off         | Supply current when off (sleep mode) | _    | 10   | 50   | μΑ     | Vin1(2) = 0V, Vcc=12V  |

| Icc on          | Supply current when on               | _    | 8    | 12   | mA     | Vin1 = 5V              |

| Vdgl            | Low level diagnostic output voltage  | _    | 0.4  | _    | V      | ldg = 1.0mA            |

| ldg leakage     | Diagnostic output leakage current    | _    |      | 10   | μΑ     | Vdg = 4.5V             |

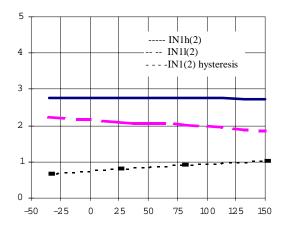

| Vih1 (2) th.    | IN1 (IN2) high threshold voltage     | _    | 2.6  | 3.4  | \<br>\ |                        |

| Vil1 (2) th.    | IN1 (IN2) low threshold voltage      | 1.0  | 2.0  |      | V      |                        |

| lin1 (2)        | ON state IN1 (IN2) positive current  | _    | 30   | 80   | μΑ     | Vin1, 2 = 5V           |

| Vccuv+          | Vcc UVLO positive going threshold    | _    | 5    |      |        |                        |

| Vccuv-          | Vcc UVLO negative going threshold    | _    | 4    |      | .,     |                        |

| Vss+            | SS high level threshold              | _    | 4.2  | 4.8  | V      |                        |

| Vss-            | SS low level threshold               | 0.8  | 1.2  |      |        |                        |

| Iss leakage     | SS pin leakage current               | _    | 0.1  | 10   | μΑ     | Vss = 5V               |

| Vrc             | Typical voltage of the Vrc pin       |      | 5.3  |      | V      | Irc = 0.25mA           |

| IN1(2) hys      | IN1 (2) input hysteresis             | 0.2  | 0.7  | 1.5  |        | lin = 1mA              |

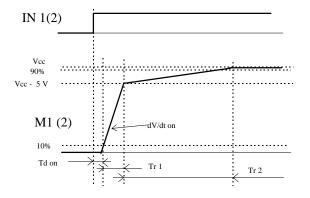

# **Switching Electrical Characteristics**

$V_{CC} = 14V$ , Resistive Load = 3.0 $\Omega$ ,  $T_i = 25^{\circ}$ C, (unless otherwise specified).

| Symbol             | Parameter                                                      | Min. | Тур. | Max. | Units | <b>Test Conditions</b>   |  |

|--------------------|----------------------------------------------------------------|------|------|------|-------|--------------------------|--|

| Tdon               | Turn-on delay time                                             | _    | 55   | 100  |       |                          |  |

| T <sub>r1</sub>    | Rise time to Vout = Vcc -5V                                    | _    | 3    | 30   | μs    |                          |  |

| Tr2                | Rise time from the end of Tr1 to Vout = 90% of V <sub>CC</sub> | _    | 40   | 200  |       | see figure 3             |  |

| dV/dt (on)         | Turn ON dV/dt                                                  | _    | 3    | _    | V/µs  |                          |  |

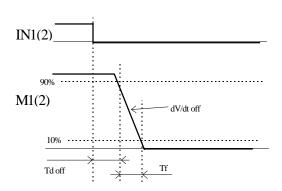

| Tdoff              | Turn-off delay time                                            | _    | 30   | 80   |       |                          |  |

| Tf                 | Fall time to Vout = 10% of Vcc                                 | _    | 16   | 50   | μs    | see figure 4             |  |

| dV/dt (off)        | Turn OFF dV/dt                                                 | _    | 2    | _    | V/μs  |                          |  |

| IN1 (2) max. freq. | Max. frequency on IN1 (IN2)                                    | _    | 500  | _    | Hz    | dt=0.5                   |  |

|                    |                                                                |      |      |      |       | none braking mode(2)     |  |

| Soft-Start freq.   | Soft-Start oscillator frequency                                | 15   | 22   | 30   | kHz   |                          |  |

| Ig1 (2) min.       | Min. Gate 1 (Gate 2) current                                   | 50   | 80   | _    | mA    | low side driver          |  |

| Trd                | Min. IN1 (2) OFF time to reset SS                              | _    | 8.0  | _    | ms    | C=3.3 $\mu$ F, IN1 = IN2 |  |

| Vg1                | Gate 1 (gate 2) voltage                                        | _    | 7    | _    | V     |                          |  |

| Tin1 (2)           | Minimum IN1 (2) ON state for operation                         | 200  | 350  | 550  | μs    |                          |  |

| Vst                | Shoot-through protection threshold                             | 1.1  | 2.3  | 3.3  | V     | See AN-1032              |  |

#### **Protection Characteristics**

| Symbol | Parameter                  | Min. | Тур. | Max. | Units | Test Conditions |

|--------|----------------------------|------|------|------|-------|-----------------|

| Tsd    | Over-temperature threshold | _    | 165  | _    | °C    | See figure 2    |

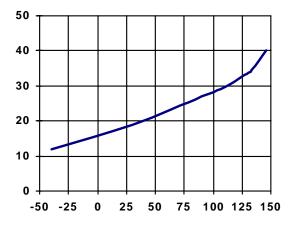

| Isd    | Over-current threshold     | 24   | 30   | 38   | Α     | See figure 2    |

| Treset | Reset time                 | _    | 100  | _    | μS    | IN1 = IN2 = 0V  |

Note 1: The low side switches present sufficient cooling capability in order to have the whole H Bridge function protected by the IR3220S inner temperature sensor.

Note 2: Switching in the none braking mode consists in cycling one of the inputs while the other one is held at the high logic level.

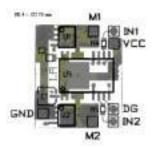

## **Lead Definitions**

| Vcc | Positive power supply                       | IN1 | Logic input 1 ( Leg 1 Cdt. / mode )            |

|-----|---------------------------------------------|-----|------------------------------------------------|

| M1  | Motor 1 output (high side source - leg 1)   | IN2 | Logic input 2 ( Leg 2 Cdt. / mode )            |

| M2  | Motor 2 output ( high side source - leg 2 ) | Dg  | Diagnostic output ( open drain )               |

| G1  | Gate 1 drive output (low side gate - leg 1) | Vrc | Voltage ref. output (soft-start RC)            |

| G2  | Gate 2 drive output (low side gate - leg 2) | SS  | RC soft-start input (the voltage on this input |

| Gnd | Power supply return                         |     | drives the switching duty cycle )              |

# **Lead Assignments**

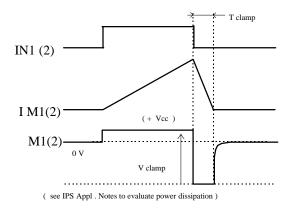

Figure 1 - Active clamp waveforms

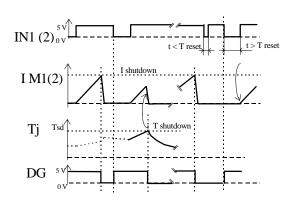

Figure 2 - Protection Timing diagram

Figure 3 - Switching Time Definitions (turn-on)

Figure 4 - Switching Time Definitions (turn-off)

Figure 5 - IN1 (2) thresholds (V) vs Tj (°C)

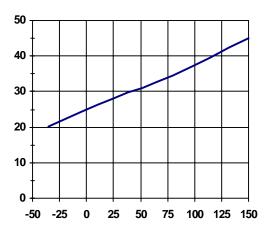

Figure 6 - IN1 (2) current ( $\mu$ A) vs Tj (°C)

Figure 7 - Iccoff (μA) vs Tj (°C)

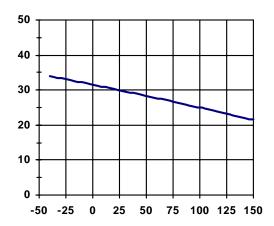

Figure 8 - Typ. I shutdown (A) vs Tj ( $^{\circ}$ C)

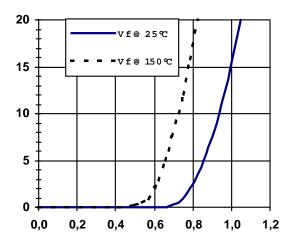

Figure 9 - Body diode : Ids (A) vs Vds (V)

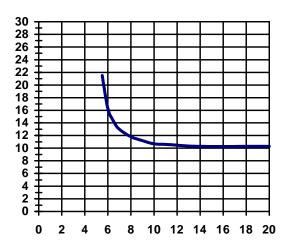

Figure 10 - Rds(on) (m $\Omega$ ) vs Vcc (V)

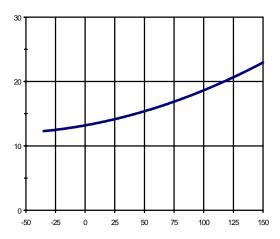

Figure 11 - Rdson (m $\Omega$ ) vs Tj (°C)

Figure 12 - Max. Cont. current (A) vs Amb. Temp. (°C)

Figure 14 - Isd (A) vs Time (s)

#### Case Outline - 8 Lead SOIC

#### **Case Outline**

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

Data and specifications subject to change without notice. 9/18/2003